|

|

|

||

当サイトはSPAM対策等のためJavaScriptを使っています。

JavaScriptの実行を可能な状態にしてご利用下さい。

Please enable the execution of JavaScript!

【PDM (Pulse Density Modulation)回路設計の基礎】 |

||

|

【DSP & FPGA デザイン ワークショップ 2008】 【リンクフリー】 私設研究所ネオテックラボ Neo-Tech-Lab.co.uk 【記載者】 【私設研究所Neo-Tech-Lab】 上田 智章 |

講演日 2008/12/12 作成日 2008/12/12 追 記 2008/12/20 最終更新日 2010/03/20 |

ここにチェックボックス型外部コンテンツ・メニューが入ります。 | ||

|

|

|

||

|

以前の関連ドキュメント メニューに戻る 無償のQuartus II Web Editionのダウンロード Alteraホーム |

|

|

A/DコンバータやD/Aコンバータ等のアナログ専用ICを使わずに、 汎用オペアンプとロジックだけで計測システム回路を構成する手法を紹介します! 【名称】DAコンバータおよびADコンバータ【発明人】上田智章【番号】特開2008-17239 ☆☆☆特許第4496493号 (登録日 平成22年4月23日)☆☆☆ (明細書作成だけでなく、全ての手続きを自分で実施したものだったのでとても嬉しい。)  ☆上記実施例は赤外線脈波、3軸加速度の4chアナログ信号のモニターを本手法で製作した事例です。10ビット、25kSPS、4chのPDM A/Dコンバータ、ZigBeeシリアル通信用調歩同期シリアル通信の送受信部等をロジックで構成。EPM570T100C5、オペアンプ3個程度で製作しました。 |

|

|

◆ハードウェア設計エンジニアの悩みは尽きない?! 図1にアナデジ混在基板を開発する場合の悩みをまとめてみました。 最近、 「プリント基板に実装していたA/Dコンバータが製造中止予定になってしまった」 「手頃な価格のワンチップ・マイコンがあるんだけど、D/Aコンバータのチャンネル数が足らないんだよね。」 「同期検波回路を使えば高精度になるんだけど、アナログ回路の規模が大きくなってコストが合わない。」 「ソフトウェア開発をやり直したくないからEmbedded Processorを採用したいんだけど、A/DやD/Aを外付けするのではメリットがないしね。」 などの声をハードウェア設計エンジニアらから聞く機会が増えてきました。 実際、大量生産されているメモリや汎用ワンチップ・マイコンと違って、A/Dコンバータをはじめとするアナログ関連ICの市場は限られているにもかかわらず、その品種は多過ぎます。それ故、採算が合わないと判断されたA/Dコンバータ 等が製造中止となる確率は他の電子部品と比べて高いようです。しかし、携帯電話やエアコンなどの用途に合わせて大量生産されているワンチップ・マイコンをコスト優先で選択すると、どうしてもA/DやD/Aの仕様が合わずに 外付けで追加のA/DやD/Aを実装する必要が出てしまい、コストが合わなくなる事例も多いようです。 ワンチップ・マイコンは確かに著しい進歩を遂げています。12bitのA/DコンバータやD/Aコンバータ、数チャンネルのPWMを搭載した低価格マイコンもあります。しかし、16bit精度のA/DコンバータやD/Aコンバータが必要なアプリケーション、複数チャンネル同時A/Dサンプリングを要求するアプリケーション、あるいは複数のボーレートの異なるUARTを使ったシリアル通信の中継などソフトウェア処理では追いつかないアプリケーションなどもあり、コストと仕様の両立に頭を悩ますことが多いと思います。 そこで、今回は、汎用オペアンプとCPLD/FPGAのディジタル・ロジックだけでアナデジ混在基板を構成する手法のひとつとして、パルス密度変調 (PDM : Pulse Density Modulation)型回路を使う方式をご紹介したいと思います。これは私が20年程前に標準ロジックやPLDを使って試作品を作る際に使ってきた手法を基に発展させたものです。近年のCPLD/FPGAの普及によってこの技術が利用しやすい環境も整ってきていることと、Web上に誰も書いていないようなので公開することにしました。図2のようなシステムやA/DやD/Aを実装したEmbedded Processorを構成するのに役立つと思います。製作事例として趣味で製作した赤外線脈波+3軸加速度 ZigBeeワイヤレス・モニターもご紹介します。 |

下図はShift + クリック で拡大します。 図1 アナデジ混在基板開発上の悩み 図2 PDM技術で可能なシステム構成例 A) B) 赤外線脈波+3軸加速度 ZigBeeワイヤレス・モニター Altera CPLD Max II EPM570T100C5N * 4ch 10bits 500SPS PDM A/Ds (3軸加速度センサ+赤外線脈波) * 2ミリ秒タイマー *115200bps調歩同期式シリアル通信 (送受信回路) *8bits PDM D/A (赤外線脈波回路のオフセット調整) * 17bits DFL+7bit電子ボリューム (ボリューム付周波数可変ブザー) 補足)電子ブザーと赤外線脈波回路のオフセット調整回路は省略あるいは簡素化が可能なので、240LEs程度に収まると考えられる。 |

|

1.パルス密度変調(PDM : Pulse Density Modulation)型D/Aコンバータ 図3にパルス密度変調(PDM : Pulse Density Modulation)方式のD/Aコンバータの基本構成ブロック図を示します。ディジタル回路部分はクロック毎に加算結果がフィードバックされる累積加算器と桁上がり(キャリー)信号をクロック毎にホールドするレジスタで構成されています。加算器の演算幅を変えることで2nbits単位の分解能を持ったD/Aコンバータを実現することができます。パルス密度変調(PDM)とは、数値に対応した確率密度で状態"0"と状態"1"のパルスを一定のクロック周波数単位で出力し、その出現密度比で多値を表現する方式です。図4上側に正弦波(サイン波: sine wave)に対応するPDM出力を例示します。ご覧のように状態"0"と状態"1"の2値しか出力されていませんが、周期的に"0"の多い部分、"0"と"1"がほぼ同数で出現する部分、"1"の多い部分が繰り返し周期的に出力されていることがわかると思います。このPDM出力をアナログ信号に変換するには簡単なロー・パス・フィルタ (LPF : Low Pass Filter)を通すだけで済みます。図4の上側のPDM信号は極めて高い周波数成分を持った2値パルス信号ですが、ある一定時間内における状態"1"の密度変化を取り出すには図3下側の図のようにLPFを用いて高周波ノイズ成分をカットするだけなのです。LPFを使って移動平均値を取り出し、パルス密度をアナログ値に変換できるのです。ノイズ成分を含まない高精度なアナログD/A値を得ようとすればカットオフ周波数を情報帯域幅にできるだけ近づけて急峻なカット特性を持ったフィルタを使うことが好ましいのですが、単純なRCフィルタでもそこそこきれいなアナログ出力を得ることができます。この不要なノイズ成分を除去する目的のLPFはノイズ・シェーピング・フィルタと呼ばれます。 PDM信号は既にiPodなどのディジタル・オーディオでは当たり前のように使われている信号形式なのです。(民生方式では∑⊿方式と呼ばれる1bitA/Dで変換されたPDM信号を用いているだけで、任意のバイナリ値に対応したパルス密度を直接変換はしていません。) |

図3 図4 |

|

●PDM D/Aコンバータの基本構造と動作原理について 図5を使ってPDM D/Aコンバータの基本回路の動作を説明します。まず、累積加算器のビット幅が2bitの場合について説明します。2bit幅の累積加算器の演算結果が取りえる値は0,1,2,3の4通りです。 D/A設定値が0なら何回0を足しても累積加算値は変化しないのでいつまでもオーバーフローを起こすことはありません。従ってPDM出力をホールドするレジスタの出力はいつまでも状態"0"のままです。 ところが、D/A設定値が1なら4クロックに1回オーバーフローを起こし、演算結果は0に戻ります。オーバーフローのタイミングで桁上がり(キャリー)信号が出力されるので、PDM出力をホールドするレジスタは4クロックに1回の頻度で状態"1"を出力します。 D/A設定値が2ならオーバーフローは4クロックに2回 (2クロックに1回)の頻度となり、D/A設定値が3なら4クロックに3回の頻度で状態"1"を出力します。 このように累積加算器のビット幅を変えるだけで非常に少ない回路規模でPDM型D/Aコンバータを実現することができます。 追記1) 2008/12/13記入 PDM D/Aコンバータはパルス密度の出現頻度を変えるD/A出力ですから、16bits精度を実現する場合には最大で3kSPS程度でしか利用できませんが、精度を落としても良いアプリケーションではノイズ・シェーピング・フィルタのカットオフ周波数を高く設定しておき、8bits精度なら最大788kSPSでの利用を行うことも可能です。これは他方式のD/Aコンバータにはない特徴のひとつです。 追記2) 2008/12/13記入 2nbits幅の累積加算器にキャリー入力を持った加算器を採用することで0から2nまでのD/A値を出力することが可能になります。普段、D/Aコンバータの出力値を0から2n-1の範囲とするときはキャリー入力を"0"とします。しかし、D/Aコンバータの出力値として2nを出力するときは、D/A設定値を最大の2n-1をセットして同時にキャリー入力を状態"1"とすることでクロック毎に必ずオーバーフローを起こして連続的に状態"1"を出力することができるからです。このキャリー入力をD/A設定値の最上位ビットとみなすことで出力可能範囲をフルに設計することができます。 上記の2bit幅の累積加算器の例ではD/A設定値3のとき、キャリー入力を"1"とすれば4クロックに4回の頻度で状態"1"のパルスを出力することができます。 |

図5 |

|

●PDM D/Aコンバータに必要な外付け回路の例 図6にPDM D/Aコンバータの外付けアナログ部分の回路設計事例を例示します。 図6上段は抵抗R、コンデンサC、ダイオードDからなるもっとも簡単なRCフィルタのケースです。ダイオードDは一見不必要に見えるかもしれませんが、これは電源がOFFになった場合にコンデンサCに電荷が残ると、CPLD/FPGAで構成されたPDM D/Aコンバータのディジタル回路のピンに電源電圧(電源OFF時は0V)より高い電圧がかかり、最悪デバイスが破壊される恐れがあるためにチャージされた電荷を放電させるための対策です。 図6下段に簡単なオペアンプで構成するLPFを例示します。 カットオフ周波数を設計するための式は図6中に記載しておりますので参考にしてください。 |

図6 |

|

●民生機器で採用されているその他の簡易なD/Aコンバータの方式とその限界 図7に既存の民生機器において比較的採用されていることが多い簡易D/Aコンバータの事例を紹介します。 図7左側は、ラダー抵抗と呼ばれる抵抗ネットワークとボルテージ・フォロワと呼ばれるオペアンプを組み合わせたディスクリートD/Aコンバータの例です。個別の抵抗を実装するのであれば精度はせいぜい1%程度でしょう。集合抵抗素子を用いれば0.1%程度まで精度は改善できるかもしれません。従って、8bitsから10bits程度のD/Aを構成するために用いられていることが多いようです。しかし、出力ピンも沢山使ってしまう欠点もあります。 秋月電子通商のDDSキットでもこの方式が採用されていました。(リンク先の写真でWellpine社のICの右横に実装されているのが集合抵抗です。10bitsのD/Aを実現していました。但し、オペアンプは使わず、FETを使っていました。) 図7右側は、様々な民生機器のプリント基板で実際に目にすることが多いPWM (Pulse Width Modulation)を使った方式です。PWM型D/Aコンバータとは、キャリア周波数を固定して、各周期には状態"0"と状態"1"を必ず同居させる必要があります。出現時間比を変えることで任意値を表現する方式です。PDM方式と同様にRCまたはオペアンプを用いたLPFフィルタを使います。 |

図7 |

|

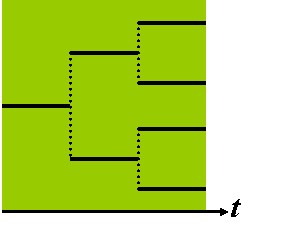

●PWM (Pulse Width Modulation)とPDM (Pulse Density Modulation)の違い 図8にPWM (Pulse Width Modulation)とPDM (Pulse Density Modulation)の違いを示します。 PWMとはパルス幅変調とも呼ばれます。キャリア周波数と呼ばれる固定周期内には必ず状態"0"と状態"1"の2状態が存在します。この"0"と"1"の時間幅を変えることで任意の値を表現します。例えばキャリア周波数を20kHzとします。もし12bitsの分解能でパルスの幅を変化させようとすればキャリア周波数よりも212=4096倍のクロック周波数でカウンタを動作させて、カウンタ値としきい値(D/A設定値)をクロック毎に比較して一致するタイミングで状態"0"から状態"1"に(またはその逆)変化させるのです。すなわち、81.92MHzでカウンタを動作させていますが、常にキャリア周波数成分が出力信号中に含まれるため、キャリア周波数よりも十分低い周波数でないと十分なノイズ成分の分離を行うことができません。 これに対して、PDMはキャリア周波数を持たず、ビット・レートを固定し、1ビット分の時間に状態"0"か状態"1"のパルスを出現させて、その出現確率で任意の値を表現します。従って、周波数の低い成分程、多くのビットのデータを使った出現頻度での表現が可能になるため、低周波なら24bitでも容易に実現することができます。従って、81.92MHzのクロックを使えば12bits精度なら20kSPSでの出力が可能です。勿論、ノイズ・シェーピング・フィルタ(LPF)のカット・オフ周波数を下げてより高精度な多値表現も可能になります。 ロジック回路の規模はPWMとPDMではそれほど変わらないのですが、原理的な差異から性能的には大きな差異を持っています。PWMでは常に状態"0"も状態"1"も持たねばならないので0及び2n-1のフルスケールの値は表現することができません。 |

図8 |

|

●基本構造PDM D/Aコンバータの設計例 図9に基本構造を持ったPDM D/Aコンバータの設計例を示します。この設計事例ではPDMoutだけでなく、nPDMoutという反転ロジックの出力も持っています。これはユニポーラ出力(例えば0Vから3.3Vまで)で使用する場合にはPDMoutだけをLPFに供給して使用するのですが、図9左下の例のようにバイポーラ出力(例えば±3.3V)を実現する場合にはPDMoutとnPDMoutをそれぞれ別のLPFに供給してから差動増幅器で差を取って使います。 図9の設計ではせいぜい100MHzくらいまでしか動作しないと思います。CPLDやFPGAの性能をフルに発揮したい場合には以下の設計を参考にしてください。ANDとNANDを使って同一のクロックから位相の揃った反転クロックを得ているところが高速化のキーポイントです。 ■8bits PDM D/Aコンバータのロジック回路設計例 Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、19LEs(Logic Elements) 最大動作可能周波数(PDMclockのfmax) 229.73MHz (最大900kSPS) (注:ユニポーラ出力として使う場合はPDMoutのみ使います。nPDMoutは使用しません。この場合、18LEs) ■12bits PDM D/Aコンバータのロジック回路設計例 Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、27LEs(Logic Elements) 最大動作可能周波数(PDMclockのfmax) 201.09MHz (最大49kSPS) (注:ユニポーラ出力として使う場合はPDMoutのみ使います。nPDMoutは使用しません。この場合、26LEs) ■16bits PDM D/Aコンバータのロジック回路設計例 Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、34LEs(Logic Elements) 最大動作可能周波数(PDMclockのfmax) 201.09MHz (最大3kSPS) (注:ユニポーラ出力として使う場合はPDMoutのみ使います。nPDMoutは使用しません。この場合、35LEs) |

図9 |

|

●任意分解能のPDM D/Aコンバータを実現する方法 ここまで読まれた読者の中には 「このD/Aの絶対精度は?」 「ゲイン調整が必要だから結局既存方式と価格的に大差ないのでは?」 等の疑問をお持ちの方がおられると思います。 確かにこれまでにご紹介した基本構造のPDM D/Aコンバータは簡易なRCフィルタを用いる場合にはコンデンサの並列抵抗Rp成分によって放電が生じるので微妙に最大値を出すことはできないでしょう。しかし、この欠点はPWM方式でも同じです。 それよりもアプリケーションで常に問題となるのは、 「ちょうど1degitを1ミリボルト、あるいは500マイクロボルトになるように調整したい」 という測定レンジを合わせこむ必要があるケースなのです。 しかし、大半の既存A/Dはこのような用途に対応することができません。 つまり、既存A/Dコンバータでは例えば0~2.5Vを12bitで分割してあるので、外付けアッテネータかゲイン調整アンプでちょうど1degitが入力の基本分解能(例えば1mA、0.01℃、角度0.2度、0.2N、10m/秒等)になるように調整する回路が必ず別途必要になってしまうのです。この調整にはトリマ抵抗が付きものになってしまいますが、抵抗体接触面の酸化等の理由で長期使用すると調整がずれておかしな値となるトラブルのもとになる場合があります。電子ボリュームを採用すれば接触面がなくなるので、この問題は解決しますが、コストは大幅にアップしてしまいます。そうでなければ、ソフトウェアで変換を行ってユーザーがわからない単位(例えば、1/2048ボルトとか、1/65536アンペア等)で変換していることを隠ぺいするしか方法がなかったのです。 PDM型D/Aコンバータは、累積加算値と桁あふれを検出する最大サイズとを常に比較して桁あふれの判定を行うことで、任意の分解能を持ったD/Aコンバータを実現することができる特徴を持っています。図10左上にそのアルゴリズムを示します。 ステップ1で a=sum+vDA を実行して累積加算値sumにD/A設定値vDAを加算した仮の累積加算結果aを得ます。 ステップ2で b=a-vMaxを演算して分解能最大値vMaxを超えて桁あふれを引き起こすか否か調べます。 減算結果はボロー(borrow)(結局、減算器は加算器と同じ演算器を使うのでキャリー出力)に反映されるので、ボロー(borrow)の結果に基づいて、a<vMaxならsum=aとしてPDMout=0[桁あふれ(キャリー)なし]とするか、a≧vMaxならsum=bとしてPDMout=1[桁あふれ発生]とします。 図10左下のブロック図に示すように1つの演算器(加減算器)を2サイクルで使い、上記のアルゴリズムを実行します。最大100MHz周期で動作させることができます。 この任意分解能タイプのPDM型D/Aコンバータを使えば、図10右に示すようにちょうど3Vが3000digitsあるいは30000digitsとなるように調整することも容易です。また、vMaxを変更することで感度を変更することもできます。 この構造により、PDM型D/Aコンバータは従来にない特徴を備えたD/Aコンバータとなります。これまで計測用途では必ず必要でトラブルのもととなっていたトリマ抵抗やゲイン調整回路を省略することができます。 |

図10 |

|

2.PDM型電子ボリューム 上記で紹介した任意分解能タイプのD/Aコンバータだけですべてが解決するわけではありません。 乗算器や電子ボリュームを用いずに信号振幅を調整したいといった用途もあります。 ここではパルス密度変調 (PDM : Pulse Density Modulation)の特徴を最大限に利用したPDM型電子ボリュームを紹介します。 ●PDM型電子ボリュームの基本原理 図11上段にパルス密度変調 (PDM : Pulse Density Modulation)型電子ボリュームの基本回路構成を示します。 PDMではパルスの"1"の出現頻度を確率的に(あるいは一定割合で)減らすことで簡単に電子ボリュームを実現することができます。図11上段のブロック図は設定値と累積加算器のビット幅で決まる割合で状態"1"の通過頻度を変更するコンセプトに基づいた設計事例です。PDM入力が状態"1"の場合にのみ回路を動作させ、設定値を累積加算させて桁あふれを起こすか否かでPDM入力を通過させるか否か決めるものです。 当然、設定値(ボリューム値)が大きいほど桁あふれの確率頻度が高くなり、反対に小さいほど状態"1"パルスの通過頻度が抑えられます。 図11下段に5bitsPDM型電子ボリュームでパルス密度変調された正弦波信号を通過させた場合の実験結果を例示します。確かに原理通り機能することがご理解いただけるものと思います。 既にお気づきの方もおられるでしょうが、このPDM型電子ボリュームは乗算器としても機能しています。まともにバイナリで演算すると大規模になってしまう様々なフィルタ処理(DSP)もパルス密度変調(PDM)を施して1bitの信号に変えてしまうことで乗算が加算演算で実現してしまうのです。これはPDMの最大特徴の一つと言えます。特に、PDMに対して±1を掛ける同期検波回路の乗算器のような用途なら排他的論理和(XOR : exclusively OR)1つで、(すなわち1LEで!)実現してしまうのです。

|

図11 |

|

●PDM型電子ボリュームの設計例 図12にPDM型電子ボリュームの基本形の回路設計事例を紹介します。この5bitsのPDM型電子ボリュームを使って図11下段の結果を得ました。この設計例では、ボリューム設定値を可変値にせず、半固定値(constant)にしています。ゲイン調整など計測器の分野などではトリマ調整を行うアプリケーションがありますが、このような場合に図12の事例が適していると思います。勿論、ビット幅を変えるだけで簡単に仕様変更できます。 下にボリューム設定値をレジスタに保存するようにした可変ボリュームの設計事例を紹介します。極めて小規模のLogic Element数で実現できることがわかるでしょう。 ■6bitsPDM型電子ボリュームの設計事例 Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、22LEs(Logic Elements) 最大動作可能周波数(PDMclockのfmax) 167.22MHz |

図12 |

|

3.PDM型A/Dコンバータ ここまで読み進まれた方はもう既にPDM型D/Aコンバータを使ってA/Dコンバータを実現できることにお気づきかもしれません。実際、実在するA/Dコンバータの大半は、内部にD/Aコンバータを組み込んでいるからです。 ●比較フィードバック型PDM A/Dコンバータ 図13Aの1)に、PDM型D/Aコンバータと、アップダウン・カウンタと、コンパレータ(汎用オペアンプで可)からなる最も簡単な構造のトラッキング型A/Dコンバータを例示します。アップダウン・カウンタから出力された値をPDM型D/Aコンバータから出力して、外部アナログ入力とコンパレータで比較し、外部アナログ信号の方が大きければカウンタ値をインクリメント、反対に外部アナログ信号の方が小さければカウンタ値をディクリメントするという簡単な構造です。当然、比較の1ステップ単位で±1しかA/D変換値を変化することができないのでスルーレートが遅い欠点がありますが、外部アナログ信号の情報帯域が狭いケース(温度、生体信号等)には十分役立ちます。また、A/D変換時間が極めて短いのも特徴のひとつです。 ■10bits PDM型A/Dコンバータの設計事例(4ch同時サンプリング) Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、22LEs(Logic Elements) 最大動作可能周波数(PDMclockのfmax) 160.05MHz PDM型D/AコンバータのD/A設定値を保存するレジスタをUp/Downカウンタに変更し、外部コンパレータからの大小判定フラグを一時格納するレジスタを追加しただけの構造です。勿論、このA/Dコンバータを使うには外部に若干のコントロール回路が必要です。下の例を参考にしてください。本事例ではパソコンにデータを引き込んだ際に処理しやすいように、上位に6bitを付けたして16bitにして出力しています。多チャンネルのシステムを作る場合には上位のbitをチャンネル番号として割り当てることもできます。  ●バイナリツリー探索型A/Dコンバータ 既存A/Dコンバータの中で最もポピュラーなのがこのタイプでしょう。バイナリツリー(二本木)探索法とは、A/D変換時間の短縮のため、第一ステップでは、入力範囲の1/2の値をD/Aコンバータから出力し、仮にそのレベルよりもアナログ入力が大きければ、上半分の中央値(すなわち3/4)を、反対にアナログ入力が小さければ、下半分の中央値(すなわち1/4)をというように、常にに探索領域の中央値をD/Aコンバータから出力して比較していく方法です。  ●逐次比較型A/Dコンバータ 既存A/Dコンバータの中で最も製造中止率が高いのがこの方式でしょう。14bits程度のA/Dコンバータでも数千円はしていました。現在はほとんど見かけることはなくなりました。 図13Aの2)に構造を例示します。これを実現するには、アップ・カウンタ(またはダウン・カウンタ)にクロックを常に入力してカウンタ値をインクリメント(またはディクリメント)させてカウンタ値をのこぎり波状に変化させます。カウンタ値をそのままPDM型D/Aコンバータに入力すれば、アナログののこぎり波に変換することができます。これを外部アナログ信号と比較してコンパレータのフラグが変化する瞬間のカウンタ値をA/D値としてレジスタに記録させるだけで実現できます。 ●変化量可変方式比較フィードバック型A/Dコンバータ 比較フィードバック型では1クロックでは1degitしか変化させることができません。このためスルーレートが著しく遅いという欠点を持っています。より高速なA/Dコンバータを実現するために考えられる1つの回答が、コンパレータの大小判定フラグの履歴を使って探索幅を増減させるというアイディアです。10数年ほど前に筆者も超電導量子干渉素子(SQUID : Superconducting QUantum Interference Devices)を用いた超高感度磁気センサの電子回路でこの方法を試しました。それをご紹介いたします。 探索幅を±1degitから±ndegitsまで変化できるようにアップ・ダウン・カウンタを設けます。コンパレータからの判定フラグが同じ結果が続いたら探索幅が狭すぎると判断して探索幅を増加させます。反対にコンパレータからの判定フラグが1クロック毎に反転するようならアナログ入力は探索幅の範囲内にあることがわかり、探索幅を減少させます。 探索幅を±1ずつ変化させるよりも2のn乗単位に変化させた方がスルーレートを100倍以上速く改善することができました。 その他、予測符号化など様々な方式、バリエーションが考えられます。 |

図13 A) B) |

|

4.∑⊿ (シグマ・デルタ)方式A/Dコンバータ 図14に例示した回路は∑⊿(シグマ・デルタ)方式のA/Dコンバータです。最もこれはアナログ量をPDM変換して1bitの信号に変換するだけの部分ですので、A/Dコンバータとして使うにはこの後で、単位時間当たりの状態"1"パルスの数をカウントしなければなりません。外付けのアナログ回路としてはオペアンプ2個必要になってしまいますが、1パッケージに2個入りや4個入りのオペアンプICもありますので比較的コンパクトです。 アナログ回路は左側が積分器、右側がコンパレータとなっています。 原理としては、アナログ信号として-S(t)が入力しており、ディジタル側からは2値化信号O(t)が入力していると考えます。すると積分器の出力としてはE(t)=∫{S(t)-O(t)}dtが得られることになります。これは長時間の累積的誤差を意味します。この累積的誤差が基準値(通常、3.3V電源なら1/2の1.65V)と比べて大きいか小さいかで次の2値化信号O(t)を決定するのです。オペアンプとしてAD823を使った実験では10MHzクロックでも動作しました。 同期検波回路の場合なら、この方式でPDM信号に変換することをお勧めします。なんといっても1LE(Logic Element)でPDMに変換できるのですから。 この積分器のアナログ入力に接続されている抵抗(例では2kΩ)の値を変えることで簡単に入力レンジを変えることができます。抵抗値を例えば10kΩとディジタル2値化信号側の5倍にしてやれば、入力可能電圧範囲も5倍に拡大できます。また、反対にディジタル2値化信号側より小さくすれば入力バイアス電流は大きくなりますが、小さな信号振幅のままPDMに変換することができます。 |

図14 |

|

5.DFL(Direct

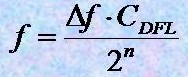

Frequency Loop) DFL(Direct Frequency Loop)とは、システム・クロックを基に任意周波数の矩形波あるいはのこぎり波を発生する回路方式です。DFLの基本回路を図15左上に示します。またしても累積加算器です。 動作を理解するために、システム・クロックとして32,768Hz=215Hzが供給されており、累積加算器のビット幅が15ビットであるとします。 この累積加算器の周波数レジスタに1が格納されている場合には1クロック毎に累積加算値は1ずつ増加していき、32768回加算する毎にオーバーフローが発生して累積加算値が元に戻ります。従って、累積加算値が格納される位相レジスタの値は図示の通りのこぎり波状に変化することになります。しかもその周期はちょうど1Hzになります。 周波数レジスタに2が格納されている場合には倍のペースで累積加算値が増加するので、のこぎり波の周期は半分になり、周波数2Hzののこぎり波が出力されます。 もうおわかりでしょう。周波数レジスタにnが格納されている場合にはnHzが出力されることになるのです。 さて、位相レジスタの最上位ビットだけを取り出せばどんな数値を入れてもほぼデューティー50%(誤差は最大1システムクロック分のみ)の矩形波が得られます。 さらに最上位から2ビット目を取り出せば倍の周波数の矩形波が、最上位から3ビット目を取り出せば4倍の周波数の矩形波を取り出すことが可能です。 一般的にはシステム・クロックをCDFL[Hz]、周波数レジスタの値を⊿f、演算器のビット幅をnビットとすれば、最上位ビットの矩形波と位相レジスタののこぎり波の周波数f[Hz]は次式で与えられます。  |

図15 |

|

●DFLを応用したボーレート・ジェネレータの例 図16にDFL(Direct Frequency Loop)を利用したシリアル通信用ボーレート・ジェネレータを例示します。このDFLによるボーレート・ジェネレータは任意のシステム・クロック(例では20MHz)から非常に正確なボーレート・クロックを簡単に作り出すことができます。特に、位相レジスタから取り出すビット位置の選択によって、調歩同期の受信回路用に4倍クロックも取り出すことができることもメリットの一つです。パソコンとの通信に用いられることが多いUARTの設計事例については後述します。 |

図16 |

|

6.DDS(Direct

Digital Synthesizer) 計測分野では測定のために正弦波出力が必要になることがよくあります。このような場合にファンクション・ジェネレータ(Function Generator)がよく使われますが、同期検波や少し込み入った測定を行おうとすると、市販品では役不足となることが多いのです。 ここでは、Altera社のCPLD (Max IIシリーズ)に内蔵されているフラッシュ・メモリをウェーブ・メモリとして用いるDDS (Direct Digital Synthesizer)の構成方法をご紹介いたします。 図17はDFL (Direct Frequency Loop)にウェーブ・メモリを直結させたDDS (Direct Digital Synthesizer)の基本構造を示しています。図中のD/AコンバータはもちろんPDM型D/Aコンバータを用いることができます。 DFLの位相レジスタ出力は図15からわかるようにのこぎり波状に変化します。この上位ビットをウェーブ・メモリのアドレスとして供給します。例えば、位相レジスタの上位9ビットを取り出した場合には、1回転360度の位相空間を512等分したことに対応するのです。ウェーブ・メモリの各アドレスには対応する正弦波の値を格納しておけばDFLの出力周波数に対応した正弦波がウェーブ・メモリから出力されるのです。 Altera社のCPLD (Max IIシリーズ)に内蔵のフラッシュ・メモリに合わせたHex形式フォーマットのデータを自動生成する方法に関してはここからダウンロード・解凍を行い、EXCELフォルダの中のExcelを参考にしてください。これは以前にやっつけで書いたトランジスタ技術の記事とその関連追加記事が元になっています。この記事では説明スペースが殆どもらえなかったのでD/Aコンバータは外付けのIC(AD1866)を使用しました。もちろん、PDM型D/Aコンバータを使えばEPM240T100C5Nたった1個でファンクション・ジェネレータが実現できたのですが、紙媒体という有限スペースでは限られた情報しか提供できなかったわけです。 |

図17 |

|

●DDSの構成例 Altera社のCPLD Max IIシリーズには8192アドレス×16ビットのユーザー・フラッシュ・メモリが内蔵されています。このメモリをウェーブ・メモリとして使うことで、シリーズ最下位のEPM240T100C5NでもDDS (Direct Digital Synthesizer)を構成することができます。図18のように構成すれば概ね120LEs程度で任意周波数の正弦波出力が行えるDDS (Direct Digital Syhthesizer)を作ることができます。さて、このメモリですが、実際にはシリアル・タイプのものが実装されているのですが、無償ツールQuartus II Web Editionのmegafunctionsの中のstorage項にはaltufm_i2c, altufm_spi, altufm_parallel等のマクロが格納されています。最初、私もaltufm_parallelを使って設計したのですが、内蔵オッシレータでタイミングを作っているために読み出し速度が不十分でした。 仕様書を読んでみると、altfm_noneというマクロでは100nS単位でタイミングを作ればアドレス9ビットをシリアル・レジスタ経由で叩き込んで、100nSで読みだしたデータをデータ入出力用シフトレジスタにコピー、さらに1ビットずつシフト出力していくことができます。アドレス・レジスタとデータ・レジスタが分かれているので、うまくパイプライン化すれば1.6μ秒で1サンプルの出力を行うことができます。 従って、正弦波1周期あたり最低でも16サンプル出力するとすれば、1波あたり25.6μ秒となるので大体40kHzくらいまでは使えるファンクション・ジェネレータを構成できることになります。これで満足できない人は外付けのSRAMあるいはフラッシュ・メモリを実装したDDSを設計する必要があります。DFL自体は24bitでも160MHz以上で動作するので10MHzくらいまで動作するDDSは作れるということになります。 |

図18 |

|

●位相調整回路を付加した同期検波用DDSの構成例 せっかくオリジナルのDDSを作るなら単なるファンクション・ジェネレータだけでは勿体ないので、同期検波回路にも利用できる位相調整機能の付いた検波用矩形波も発生できるものがよいでしょう。いろいろな計測アプリケーションでは発信周波数に同期して検波するだけでなく、倍周波に同期して検波する場合もあります。 図19に示すように、位相遅延は減算器を別に用意して位相レジスタの値から指定値を差し引くことで容易に行うことができます。DFLの項で説明したように、矩形波を取り出すビット位置を変えるだけで、倍周波数で検波するための信号も簡単に得られます。また、この位相遅延回路方式はアナログ方式と違って360度遅延できるので有利です。 ■24bits FDLの設計事例 後述のDDSで使用するDFLです。位相遅延された2倍波出力もあります。 Altera CPLD Max IIシリーズ EPM570T100C5N でコンパイル時、58LEs(Logic Elements) 最大動作可能周波数(FDLclockのfmax) 179.6MHz  |

図19 |

|

●Direct

Digital Synthesizerと同期検波用矩形波の生成例 図20はシンプルなDDS(Direct Digital Synthesizer)の設計事例です。ユニポーラでもバイポーラでも外付け回路次第で使うことができます。 ボリューム機能と基本波及び倍周波での検波用矩形波出力機能を持ったDDSの設計事例を以下に示します。 従って、∑⊿方式A/Dコンバータでアナログ信号に変換し、Exclusively OR(XOR)を乗算器代わりに使えば、このDDSと組み合わせることで同期検波を行うことができます。ディジタル値に変換したい場合には、検波後のPDM信号の状態"1"パルスの単位時間当たりの数をカウントするだけです。 直交検波回路が必要な場合でもDFLの位相値の上位2ビットに1を加えるだけで90度位相の違った矩形波を簡単に得ることができます。もし、アナログで直交検波回路を組めば数万円のコストがかかるかもしれませんが、PDM手法を使えば、EPM240T100C5N 1個とオペアンプ2個程度の回路(1000円程度)で実現できてしまうのです。 ■バイポーラ出力6bitボリューム付きDDS (total 165LEs)  Sub Modules

DFL24bit(58LEs) Wave Memory(28LEs) PDM_DAC16bit(35LEs) PDM_volume6bit(22×2=44LEs) fmax179.6MHz fmax10MHz fmax201.09MHz fmax167.22MHz |

図20 |

|

7.UART(調歩同期式シリアル通信) 最近のパソコンにはUSBとLANくらいしか外付け機器に接続する手段がありません。 しかし、FTDI社のFT232RLのように簡単にUSBをシリアル・ポートに変換してくれるICがあります。FTDI社からは無償のVCP (Virtual Com Port)ドライバとD2XXドライバが提供されており、特にVCPを使えば、USBなど全く意識することなく、Win32APIを使って通常のファイル感覚でComポートにアクセスすることができます。MicrosoftのExcelからでもこのアクセスは容易です。Win32APIについてはここに詳しく書いておりますので参考にしてください。 秋月電子通商からはFTDI社のFT232RLとその周辺回路を実装したモジュールを入手することが可能です。DIP間隔のモジュールですので、試作には極めて便利なモジュールです。 ●最もポピュラーなシリアル通信フォーマット 上記のFT232RLあるいはそのモジュール基板を使えば、図21のシリアル通信フォーマットを使って、極めて容易にパソコンとの通信を行うことができます。このフォーマットは調歩同期式通信でよく使われている形式です。データを送信し始める前にスタート・ビットの呼ばれるLowレベルが通信ボーレート1ビット分の時間出力されてから、下位ビットから順に上位ビットまで出力され、最後にストップ・ビットと呼ばれるHighレベル信号が出力されるのです。従って、8ビットのデータを送るのに必ずスタート・ビットとストップ・ビットも必要なので1バイトの転送には最低10ビット分の通信時間を要します。 通信に使われるボーレートは歴史的に技術が進歩する度に追加されてきました。以下のボーレートがよく使われています。 300BPS 600BPS 1200BPS 2400BPS 4800BPS 9600BPS 19200BPS 38400BPS 57600BPS 115200BPS 230400BPS ストップ・ビットも1ビットだけでなく、1.5ビット、2ビットのバリエーションや、D8ビットを送信する代わりに、データの各ビットを全部足すと偶数(even)となるか奇数(odd)となるかで通信エラーを検出するパリティー・チェックという機能を使う場合もあります。 しかし、多くの民生機器で使われていることが多いのは、データ8ビット、スタート・ビット1ビット、ストップ・ビット1ビットのフォーマットでしょう。 |

図21 |

|

●シリアル通信送信回路部 図21に記述された調歩同期式シリアル通信の送信回路は極めて容易に設計することができます。図22に設計事例を示します。右側の1ビットのシフト・レジスタはスタート・ビットに、中央の8ビットのシフト・レジスタはデータに、左側の1ビットのシフト・レジスタはストップ・ビットに対応しており、clockは通信ボーレート周波数の矩形波を使います。添付のシミュレーション波形からもわかるように、load信号がHighレベルのときにclockが立ち上がることで初期設定(データのパラレル読み込みとスタート・ビット、ストップ・ビットの設定)が行われます。1バイト分しか使わない場合にはSDinをVCCでHighレベルに吊あげます。複数バイトの一括送信をする場合には図22下段に記載したようにカスケード接続が簡単です。最終段のSDinはVCCでHighレベルに吊あげます。 |

図22 |

|

●シリアル通信受信回路部 図23Aにスタート・ビット、データ・ビット、ストップ・ビットの読み出しタイミングを検出する部分の回路設計事例を、図23Bにその実際の使い方の事例を示します。この回路は高速性を意識しないで設計したものですが、230,400BPS程度なら問題なく動作します。スタート・ビットの検出を精確に行うため、通信ボーレートの4倍のクロックをR4clockに供給します。常時RxDを監視してHighからLowに変化したことを検出したクロック・タイミングで6bitsのアップ・カウンタをリセットします。すると、データの最適な読み出しタイミングはカウンタの値が4, 8, 12, 16, 20, 24, 28, 32となります。図23Bの例のように、これを外付けのシフト・レジスタにイネーブルとして供給します。データの受信完了タイミングはカウンタ値が36のときとしています。

|

図23 A) B) |

|

Appendix DDSやPDMに特有の低周波揺らぎについて PDM技術というのは、結局、累積加算器の応用事例に他ならないことがわかっていただけたことと思います。 私は、1/4世紀前にダイキン工業株式会社に入社して最初の5年間は3次元グラフィックスの描画エンジンばかりを手掛けました。3次元グラフィックスのうち、グロー・シェーディングと呼ばれる描画方法は直線補間によって行われるため、結局、加算器の使い回しで機能を実現することに時間を費やしていました。テクスチャー・マッピングも加算器ですし、高速処理の可能な回路を設計しようと思えば結局加算器に頼らざるを得ませんでした。動画で遊ぶことができればもっと楽しかったかもしれませんが、分業の結果、描画エンジン部分しか研究を許されませんでした。これを5年間もやるというのははっきり言って苦痛でした。加減算くらいしか登場しない回路がどれほどつまらないものかわかるでしょう。少しでも面白みを追及した結果、PDM技術にも迷い込みました。PDMの基礎はこの段階で殆ど完成していたと言えます。ダイキン工業の研究ミッションはグラフィックスに特化されたものでしたし、当時に出現したザイリンクスのXC9000は前評判と違ってゲート・アレイと比較すると本当にがっかりするような性能だったので、この技術 は特許出願も発表することもなく、すっかり埋もれてしまいました。 また、多数の新規な計測装置の試作を行ってきましたが、その都度、データの精度やシステム構成にマイコンやDSPのしがらみを要求されたため、privateな実験回路以外ではこの技術を用いることは殆どありませんでした。なにより動作原理の説明が延々と続くのは仕事が円滑に進まない原因となりそうだったためです。 しかし、近年、無償開発ツールの提供や、十分な性能を持ったCPLDが安価に入手できることになってきました。さらに最近、出版社の編集者の人たちと雑談していて、どうもこの技術がWeb上にも見当たらないことに気づき、公開することにしました。 さて、前置きが長くなりましたが、PDM技術とグラフィックスには極めて強いつながりがあります。グラフィックスやFAXの技術の中に「拡散処理」という技術があります。これは図24のようにRGB各1ビットしか表現できなくても画像全体で濃淡表現が可能になるアルゴリズムなのですが、これもPDMと全く同じ処理なのです。ドットの描画密度で濃淡を表現しているからです。 図中の赤い楕円でマークした部分をよく見ていただくと、モアレ縞現象と呼ばれる縞模様に気づかれることと思います。これと全く同じ現象が、PDMやDDSにもあることは容易に予想していただけるでしょう。つまり、累積加算器を使って状態"1"のパルスを発生している以上、どうしてもその出現には規則性が生じてしまうのです。通常のアプリケーションではこの現象が問題になることはほとんどありませんが、制御システムにこの技術を採用すると、残差にこの揺らぎが含まれてくるため、問題となる場合が存在します。 |

図24 |

|

この問題の解決には1978年から気に入って取り組んでいるもう一つの技術、スペクトラム拡散通信の技術が役に立ちます。図25下段に17bits長m系列符号発生器を例示します。このm系列符号発生器というのは、擬似ランダム符号(擬似乱数)を簡易に発生することができます。ホワイト・ノイズのようにすべての帯域でフラットではありませんが、m系列符号は非常に広帯域の周波数成分を持っています。この擬似ランダム符号を使えば、桁上がりの規則性を見かけ上、不規則に変えることができるのです。低周波の揺らぎは広帯域に拡散され、目立たなくなります。 |

図25 |

|

8.ワイヤレス生体計測システムの事例紹介 ここまで、ご紹介したPDM (Pulse Density Modulation)技術を応用したワイヤレス生体計測システムを趣味で試作してみました。図26に示します。ワイヤレス通信には通販ですぐに入手できたベスト・テクノロジーのZigBeeモジュールのZIG-100Bを使いました。Bluetoothでも同じようなモジュールがあります。信号としては、シリアル通信でRxDとTxDだけを接続すれば動作するので製作がきわめて容易です。 以前にトランジスタ技術でJogging Monitorを製作した際に使ったサンハヤトの3軸加速度センサと改良した赤外線脈波計のアナログ信号4chを10bitのPDM型A/DコンバータでA/D変換を行います。タイマーで2ミリ秒毎に送信回路を起動して、500SPS×4ch×2バイトのワイヤレス送信を行う仕様にしました。 赤外線脈波計の原理は、血液中に含まれるヘモグロビンが赤外線を吸光する性質をもっており、脈拍によって毛細血管の太さが変わることで変化する透過光量あるいは反射光量を測定することで脈波を捕捉できるということなのです。このヘモグロビンの吸光度は酸素が結合したものと二酸化炭素が結合したものでわずかに異なります。パルス・オキシド・メーターは赤外線2波長を使って交互に測定して比率を割り出すことで血中酸素濃度を測定するセンサです。今回の赤外線脈波計の回路では、将来的にパルス・オキシド・メーターを設計する場合に備えて、850nmの赤外線LEDをパルス駆動に変えました。このため、電流-電圧変換器の変換抵抗に並列にコンデンサを接続してDC成分のみ取り出しています。

|

図26 |

|

図27に大体の回路図を示します。図27BにはCPLDにUSB-シリアル変換モジュール(FT232RL)の場合が記入されていますが、実際の回路ではここにZIG-100Bが接続されています。 また、回路図に記入されていませんが、DFLとPDM型電子ボリュームの効果を調べるためにCPLDの99番ピンと100番ピンにピエゾ型スピーカーを接続しています。CPLDにDFLと電子ボリュームを内蔵しました。 図28にプリント基板のパターン図を示します。片面基板です。オペアンプはAD823を使用しました。 CPLDのロジック自体は実験実演の都合上、計測に無関係な電子ボリューム付き可変周波数の電子ブザーやオフセット調整回路も入れたため、トータルで350LEsほど使いましたが、ぎりぎりEPM240T100C5で入るかもしれません。 |

図27 A) B) C) |

|

【CPLDの回路】 main

clock_divider2 SerialInput SerialOutput_for_CQ BaudRateGenerator115200 PDM_DAC8bit PDM_ADC10bit |

図28 |

|

9.ま と め PDM (Pulse Density Modulation)技術を使えば、CPLDと汎用オペアンプ程度で本格的な直交同期検波回路などを含んだA/Dコンバータ、D/Aコンバータ、電子ボリューム等が簡単に構成できることを示しました。実際、大学やネオテックラボでの研究に使用する回路は殆どこの技術を用いています。 (これらの本来の研究対象については知的所有権の対象ですので詳細を公開する予定はありません。)  例 しかし、PDM技術の大半は公開・公知化しましたので、私の前に先行文献がなければ問題なく、使うことができるでしょう。企業で使われたい方はご自分の責任で検索・調査を行ってください。 これらに関する技術的な質問は多忙のためクライアント以外から受け付けることは一切ありませんので、ご了承ください。大学に来られる場合も、過去に安易に質問に訪問された企業の方がおられるため、有償の技術指導という形式になります。 |

|

|

心電計に関するスライド |

|

|

赤外線脈波計に関するスライド |

|

インピーダンス・プレチスモグラフ (Impedance Plethysmograph)に関するスライド 補足)回路図はロボット・アーム制御用2ch版インピーダンス・プレチスモグラフィー(Impedance Plethysmography)のアナログ回路部です。 インピーダンス・プレチスモグラフィー(Impedance Plethysmography)とは、1対の電流印加電極間に周波数200Hz~20kHzの微弱な交流電流を印加し、もう1対の電圧観測電極間に誘起する交流電圧の振幅変化を測定することによって、呼吸、心拍出量を計測する装置です。人体に電極を貼りつけるので、落雷などの不慮の事故に対する絶縁対策などを十分に取るか、バッテリー駆動にして光ファイバー通信または無線インターフェースでパソコンと通信を行う必要があります。 この電子回路は、電子回路上級者で十分な医学知識を持った方でなければ製作をお薦めすることはできません。実際、サイン波発生、電流印加回路、同期検波など、心電計に比べて多くの回路要素を含んでいます。 (LPFはもっと簡単なRCフィルタでも可能です。) Link : 海外の文献 インピーダンス・プレチスモグラフ |

|

|

以前の関連ドキュメント メニューに戻る 無償のQuartus II Web Editionのダウンロード Alteraホーム |

|