作成日2008/08/16

AlteraのMaxIIで設計しよう!

時代錯誤の回路図によるCPLD設計

様々なアプリケーションでインターフェース回路が簡単だからという理由で、いまだに調歩同期式シリアル通信をよく使います。

ここでは、20MHzくらいのクロックから比較的精確なボーレート・クロックを作る方法を紹介します。

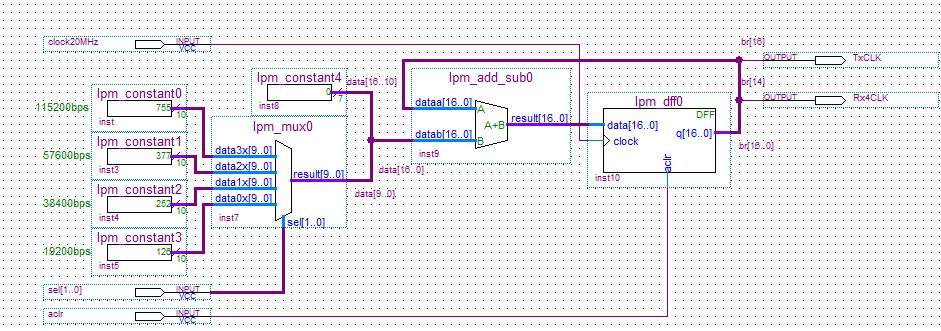

下図はDirect Digital Synthesizer(DDS)の応用回路の例です。固定クロック(例では20MHz)を供給して17bit幅の加算器により累積加算を行います。

毎回累積加算する値を妥当な値に設計することにより、累積加算値の最上位ビットをデューティー50%の精確なボーレート・クロックとすることができます。

さらに、最上位ビットから2番目のビットは2倍の周波数、最上位ビットから3番目のビットは4倍の周波数のクロックとなっていますので、調歩同期式シリアル通信の受信回路のためのクロックも作ることができます。

BaudRateGeneratorモジュールは20logic elementsです。

【設計値】

【シミュレーション結果】