【DDSの基本原理】

更新日 2006/10/28

最終更新日 2009/01/26

Page 1

このドキュメントの先頭へ

|

【DDSの基本原理】 |

更新日 2006/10/28 |

||

|

Page 1 |

|||

|

|

|||

|

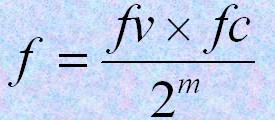

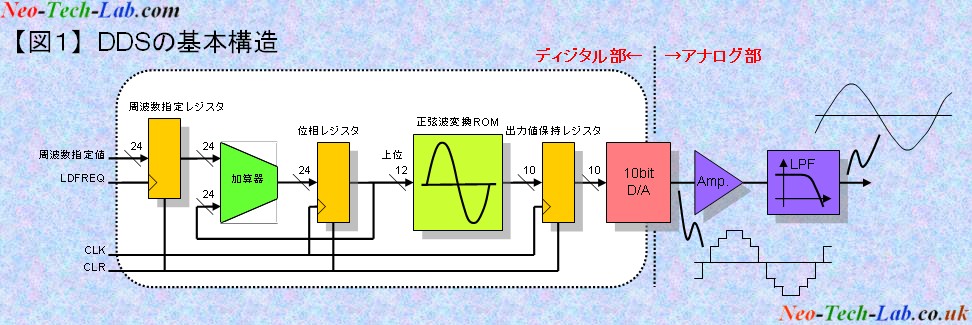

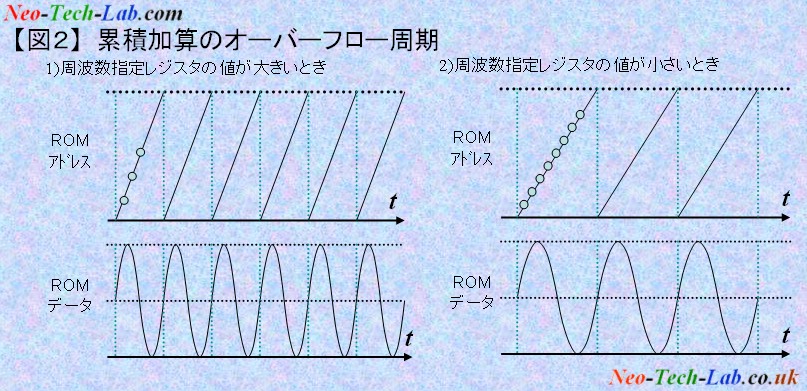

【DDSの動作原理について】 DDSとはDirect Digital Syntesizerを略記したものです。図1にDDSの最も基本的な構造を示します。内部は周波数指定レジスタ1、加算器2、位相レジスタ3、正弦波変換ROM4、出力値保持レジスタ5とD/Aコンバータ6により構成される。D/Aコンバータ6についてはAnalog Devices社のAD9832やAD9835は内蔵しているが、WELLPINE社製TC170C030AF001のように外付けで対応しているICもある。 ●私設研究所Neo-Tech-Lab.comはPDM(Pulse Density Modulation)方式のD/Aコンバータを用いる方法を提案している。この方式によれば、CPLD内部にDDSとD/Aコンバータだけでなく、電子ボリューム機能まで実装することができ、外付け回路はLPF (Low Pass Filter)を構成するため電子部品だけで済む。 次に図1の回路各部の機能を説明する。 加算器2は、外部から供給されるクロック周期毎に周波数指定レジスタ1と位相レジスタ3の値を加算処理して位相レジスタ3に結果をストアするので、位相レジスタ3には周波数指定レジスタ1の値が累積加算されてゆ く。位相レジスタ3に格納された加算結果の上位ビットが正弦波変換ROM4のアドレスとして供給されている。正弦波変換ROM4のメモリ空間には正弦波(sin波)1周期分のデータが整数値で順次記録されている。最終段のD/Aコンバータ6が符号付き整数か符号無整数かに従って記録されている正弦波のデータ型も異な る。正弦波変換ROM4も外部から供給されるクロック毎に位相レジスタの上位ビットで指定されるアドレスの情報を読み出し、出力値保持レジスタ5に結果をストアします。D/Aコンバータ6は出力値保持レジスタ5にストアされた値をD/A変換して出力します。 次に図1の回路ブロックの具体的な処理動作を説明します。 図2に示すように周波数指定レジスタ1に格納された値が大きい場合1)と小さい場合では加算器2がオーバーフローを起こす周期が異なります。 周波数指定レジスタ1、位相レジスタ3の演算ビット幅が24ビットであれば演算結果が224=16777216を超えるときオーバーフローを引き起こします。例えば、今この回路に16.777216MHzのクロックが供給されており、周波数指定レジスタ1に"1"が格納されているとすれば、16777216クロック毎、即ち1秒毎に(1Hzで)フルカウントに達し、オーバーフローが発生することになります。周波数指定レジスタ1に"2"が格納されているとすれば、先ほどとは半分のクロック数8388608クロック毎、即ち0.5秒毎に(2Hzで)フルカウントに達し、オーバーフローが発生することになります。つまり毎秒2回のオーバーフローが発生するわけです。さらに"n"が格納されている場合には毎秒n回 (nHz)のオーバーフローが発生するわけです。 累積加算結果の上位ビットが正弦波変換ROM4のアドレスとして供給されているので、出力値保持レジスタにもオーバーフロー周期で正弦波が出力されることになるのです。 以上をまとめると、累積加算部(1,2,3)の演算ビット幅がmビット幅で、外部から供給されるクロックをfc[Hz]、周波数指定レジスタ1に格納された値をfvとすれば、オーバーフローを引き起こす周波数fは次式で示されます。  ・・・・・・・・・・・・・式(1) ・・・・・・・・・・・・・式(1) |

|

|

|

|

|

|||

|

|

このドキュメントの先頭へ | ||