|

【CPLDでDDSを構成する方法】

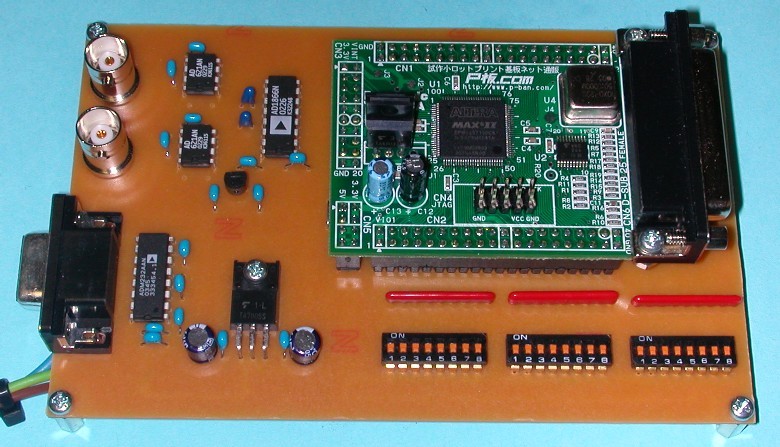

CQ出版のトランジスタ技術2006年4月号の付録はAltera社のMax

II (CPLD)を実装したプリント基板でした。このMax

IIには8192ビットのユーザーフラッシュメモリと240個のロジック・エレメント(Logic

Element)が内蔵されており、高機能なCPLDです。内蔵フラッシュメモリを活用できるアプリケーションとして、写真1、写真2に示すようなDDS

(Direct

Digital Synthesizer)を製作しました。

Pulse Density Modulation (PDM)D/Aを組み込んだ内蔵D/A方式DDSについてはこちらを参考にしてください。

【製作したDDSの仕様】

チャンネル数 1チャンネル

出力波形 正弦波

サイン波形の定義 アドレス幅 9ビット(512アドレス) データ幅 16ビット

出力電圧 ±10V

基本クロック ユーザーフラッシュメモリのオッシレータ出力を使用。 約5MHz

最小時間分解能 基本クロックを32分周。156.25kHz。

累積加算器 演算データ幅 24ビット

DIPスイッチの設定 100000H のとき 10kHzが出力されるので

最小周波数分解能 0.0095367Hzステップとなる。

【写真1】トランジスタ技術2006年4月号付録基板を使ったDDS

(Direct

Digital Synthesizer)

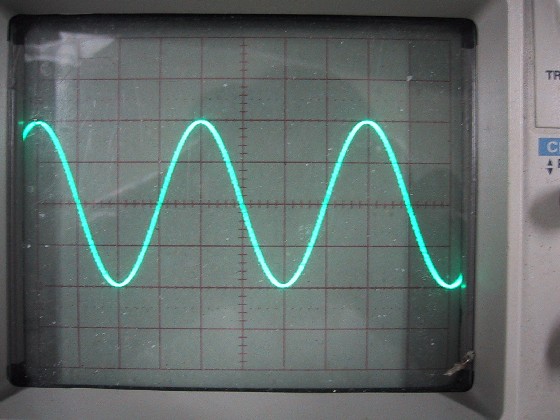

【写真2】試作基板の出力の例

|