|

【コンパイルとプログラミング】

トランジスタ技術2006年4月号付録基板の最大特徴は基板上に実装された回路によりパラレルポートをダウンロードケーブルとして利用できることです。パラレルポートを持ったパソコンがあれば開発環境が整います。

コンパイルはProcessing→Start Compilationで行います。

また、デバイスへの書込みはTools→Programmerで行います。初回のみHardware Setupを行う必要があります。

【あとがき】

今回のDDSを追試されたい方はこちらから設計情報をダウンロードしてください。

lzh形式で保存されていますので、解凍後「はじめにお読み下さい.htm」を読んでください。

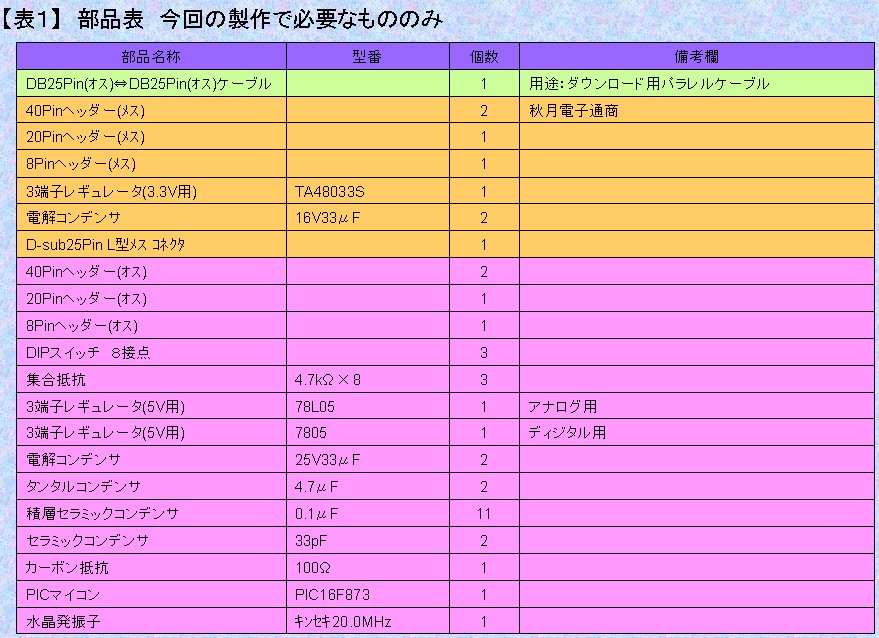

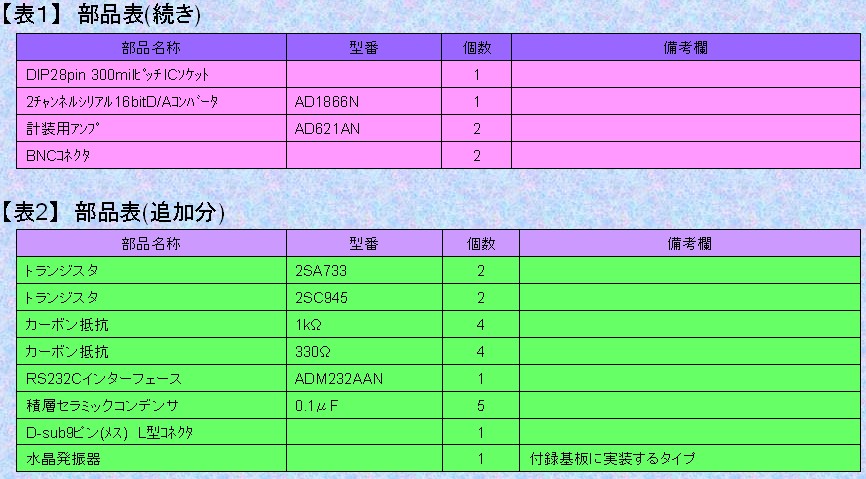

部品表は下に示します。参考にしてください。

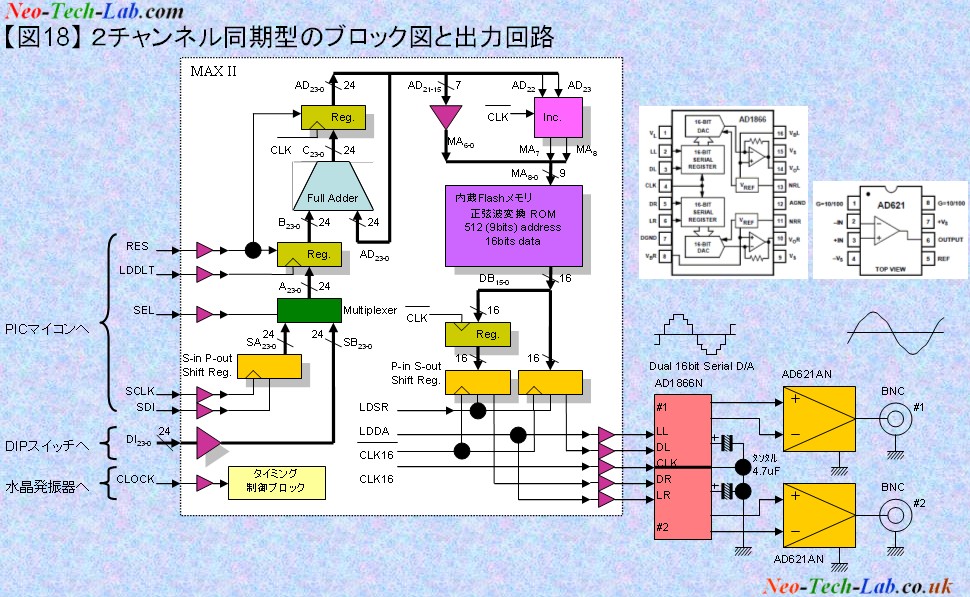

今回の1チャンネルDDSではEPM240T100C5のロジックエレメントを合計で140個(58%)使っているだけです。図18に示すように、SPIインターフェースを追加してシリアルモードとパラレルモードを持った2チャンネル同期型DDS

(sin波とcos波の同期出力)とした場合でも出力可能最大周波数は5kHzまでとなりますが75%程度のロジックエレメントで実現できます。図3の構造の延長線上にある任意位相シフトができる構造で多チャンネル設計を行っても3相同期型DDS(この場合、位相設定精度には問題があります。)が十分構成できると思います。

また、今回は内部ユーザーフラッシュメモリを用いたため最大10kHz程度までしか出力することができませんでしたが、外付けROMあるいは外付けRAMを使う構造にすれば1MHz程度まで出力できるものは容易に構成できると思います。是非、トライしてみてください。

Max IIに内蔵されているユーザー・フラッシュ・メモリを使ってもmegafunctionsライブラリのstorageカテゴリにあるaltufm_noneをクロック10MHzの2段パイプラインで使用した場合、1ワードの読み出しを1.6μ秒で行うことができます。この場合、1チャンネルのDDSなら100kHzくらいまではなんとか動作すると思います。設計情報については、調歩同期式シリアル通信回路の構成方法やPDM

(Pulse Density Modulation:パルス密度変調)型D/Aコンバータの組み込み方法とともにホームページ内で公開していますので、参考にしていただければ幸いです。

|