#### (19)日本国特許庁(JP)

G06F

## (12) 特 許 公 報 (B 2)

FΙ

(11)特許出願公告番号

# 特公平7-31598

(24) (44)公告日 平成7年(1995)4月10日

(51) Int.Cl.6 識別記号 庁内整理番号 技術表示箇所

9/28 3 1 0 D 7230-5B 9/22 350 A 7230-5B

請求項の数4(全 7 頁)

(21)出願番号 特願昭63-175780

(22)出願日 昭和63年(1988) 7月14日

(65)公開番号 特開平2-24717

(43)公開日 平成2年(1990)1月26日 (71)出願人 999999999

ダイキン工業株式会社

大阪府大阪市北区中崎西2丁目4番12号

梅田センタービル

(72)発明者 上田 智章

滋賀県草津市岡本町字大谷1000番地の2 ダイキン工業株式会社滋賀製作所内

(74)代理人 弁理士 津川 友士

審査官 斎藤 操

(56)参考文献 特開 昭61-157944 (JP, A)

#### (54) 【発明の名称】 コンピュータ

## 【特許請求の範囲】

【請求項1】供給データに対応するマッピングデータを マッピングメモリ(2)から読出してプログラムメモリ (4)に供給することにより供給データに対応するイン ストラクションを読出し、読出しインストラクションに 基づく処理を行なうコンピュータにおいて、プログラム メモリ(4)が外部媒体からプログラムメモリに存在し ていないインストラクションを取込んで少なくとも一部 の領域に格納し得るものであるとともに、マッピングメ モリ(2)が上記取込まれる各インストラクションに対 10 特許請求の範囲第1項または第2項に記載のコンピュー 応するマッピングデータを取込んで少なくとも一部の領 域に格納し得るものであることを特徴とするコンピュー タ。

【請求項2】少なくとも一部の領域が、インストラクシ ョン、マッピングデータが予め格納されていない余剰領

域である上記特許請求の範囲第1項記載のコンピュー タ。

【請求項3】プログラムメモリ(4)が、外部媒体から インストラクションを取込んでプログラムメモリ(4) の余剰領域に格納するとともに、プログラム格納アドレ スに対応するマッピングデータをマッピングメモリ (2)に格納するロードインストラクションELを有して おり、マッピングメモリ(2)が上記ロードインストラ クションに対応するマッピングデータを有している上記

【請求項4】供給データに対応するマッピングデータを マッピングメモリ(2)から読出してプログラムメモリ (4)に供給することにより供給データに対応するイン ストラクションを読出し、読出しインストラクションに 3

基づく処理を行なうコンピュータにおいて、プログラムメモリ(4)が初期化時に外部媒体からインストラクションを取込んで格納するものであるとともに、マッピングメモリ(2)が各プログラム格納アドレスに対応するマッピングデータを格納するものであることを特徴とするコンピュータ。

### 【発明の詳細な説明】

#### <産業上の利用分野>

この発明はコンピュータに関し、さらに詳細にいえば、 プログラムメモリに格納されている命令セットの変更追 10 加を行ない得るようにした新規なコンピュータに関す る。

< 従来の技術、および発明が解決しようとする課題 > 従来から提供されているコンピュータは、複雑な命令セットを実行することができるCISC (Compliment Instruction Set Computer)と単純な命令セットのみを実行することができるようにしたRISC (Reduced InstructionSet Computer)とに大別されている。

このうち、CISCにおいては、1インストラクション当り の実行時間がやや長くかかるものの、複雑な命令セット であっても実行可能であるから、仮想記憶等種々の機能 を簡単に実現することができる。しかし、プロセッサ自 体が複雑化するために、開発所要時間が著しく長くなっ てしまい、一般的には、使用者の要求に合致するCISCを 製造することが殆ど不可能になってしまうので、専門メ ーカーが提供しているCISCを使用せざるを得ないという 問題がある。そして、CISCを使用すれば、専門メーカー が提供する関連デバイスおよびアセンブラ、コンパイ ラ、デバッガ、エミュレータ等の開発ツールを用いてシ ステム設計を行なうことができるので、システム開発を 30 簡素化できるとともに開発所要期間を短くできるという 利点を有しているが、システム全体としての処理能力が 制限されてしまい、処理能力を大きくすることができな いという問題がある。

逆に、RISCにおいては、プロセッサ自体が比較的簡単な構成であるため新規なコンピュータを開発する場合の労力が比較的少なくてよく、しかも所要時間が短くなり、また、1インストラクション当りの実行時間が短くなるという利点を有している。しかし、上記の利点を達成するために、単純な命令セットのみを実行可能としているのであるから、ある程度複雑な処理を遂行させようとすれば、複数個のインストラクションを順次フェッチし、フェッチされたインストラクションを順次遂行させることが必要になるため、全体として処理を遂行するための所要時間が長くなり、この結果、処理能力が低下してしまうという問題がある。

さらに詳細に説明すると、汎用コンピュータを用いて外部データメモリをアクセスし、グラフィック処理用のハードウェアを制御する場合についてみれば、目的とする処理に適合するインストラクションが存在しない可能性 50

4

が高く、この結果、第4図(A)に示すように、インストラクションのフェッチと外部データメモリのアクセスとを多数回交互に実行しなければならない可能性が高くなる。したがって、上記インストラクションフェッチ所要時間および外部データメモリアクセス所要時間が増加し、所望の処理を遂行するための速度が低下してしまうという問題がある。そして、この問題は、実行可能なインストラクションが簡単なインストラクションのみに限定されているRISCにおいて顕著である。

しかしながら、上記汎用コンピュータにおいては、汎用コンピュータのために開発された開発ツール、アプリケーション、オペレーティングシステム(以下、OSと略称する)等のソフトウェア資産と、ペリフェラルデバイス、デバッグ用エミュレータ等のハードウェア資産とを有効活用できるという利点を有しており、しかも特にRISCにおいては、複雑な機能使用のシステムを安価に、かつ短時間で実現できるという利点を有している。

したがって、これらの利点を損なうことなく処理速度を 高めることができるコンピュータを得ることができれば 理想的であるが、特定の処理を効率よく行なうためのコ ンピュータを開発すれば汎用性がなくなってしまい、上 記の利点が損なわれてしまうことになる。

また、RISCの一種であるビット・スライス・プロセッサについてみれば、十分な処理能力を有するコンピュータを実現することが可能であるが、高機能なシステムを開発しようとすれば、ソフトウェア開発ツールが一般的に不備であるから、ソフトウェアの開発工数が著しく増加し、開発所要時間が著しく長くなってしまうという問題がある。さらに、長大なインストラクションを実行させようとすれば、インストラクションの1ワードのビット幅が大きくなるため基板面積が大きくなってしまい、コストアップを招いてしまう。

## <発明の目的>

40

この発明は上記の問題点に鑑みてなされたものであり、 汎用コンピュータが有している利点を損なうことなく特 定の処理を遂行するための所要時間を著しく短縮するこ とができ、また、所期の機能仕様を満足させるコンピュ ータを短時間で開発することができ、また、インストラ クションおよびマッピングデータを取込ませるために特 別の処理を行なう必要がなくなるとともに、外部媒体を 変更するだけで、コンピュータ自体を任意の基本命令セ ットを有する状態にすることができる新規なコンピュー タを提供することを目的としている。

#### <課題を解決するための手段>

上記の目的を達成するための、この発明のコンピュータは、プログラムメモリが外部媒体からプログラムメモリに存在してインストラクションを取込んで少なくとも一部の領域に格納し得るものであるとともに、マッピングメモリが上記取込まれた各インストラクションに対応するマッピングデータを取込んで少なくとも一部の領域に

5

格納し得るものである。

但し、少なくとも一部の領域としては、インストラクシ ョン、マッピングデータが予め格納されていない余剰領 域であればよい。

そして、プログラムメモリが、外部媒体からインストラ クションを取込んでプログラムメモリの余剰領域に格納 するとともに、プログラム格納アドレスに対応するマッ ピングデータをマッピングメモリに格納するロードイン ストラクションを有しており、マッピングメモリが上記 ロードインストラクションに対応するマッピングデータ を有していてもよい。

また、プログラムメモリが初期化時に外部媒体からイン ストラクションを取込んで格納するものであるととも に、マッピングメモリが各プログラム格納アドレスに対 応するマッピングデータを格納するものであってもよ ll.

#### <作用>

以上の構成のコンピュータであれば、プログラムメモリ が外部媒体からプログラムメモリに存在していないイン ストラクションを取込んで少なくとも一部の領域に格納 し得るものであるとともに、マッピングメモリが上記取 込まれた各インストラクションに対応するマッピングデ ータを取込んで少なくとも一部の領域に格納し得るもの であるから、外部媒体からインストラクション、マッピ ングデータを取込むことにより、開発された状態におい て遂行可能なインストラクションのみならず、新たに取 込まれたインストラクションをも遂行することができ る。また、新たに取込まれたインストラクションが使用 頻度が高いインストラクションの組合せである場合に は、一連のインストラクションを1回のインストラクシ ョンフェッチのみにより遂行させることができ、処理速 度を高速化することができる。したがって、一連のイン ストラクション数が多い場合には処理速度を著しく高速 化することができる。

また、残余の領域には開発当初のインストラクション、 マッピングデータが格納されているので、開発当初のイ ンストラクションに基く処理をも遂行することができる のみならず、関連デバイス、開発ツールを使用すること もできる。

そして、少なくとも一部の領域が、インストラクショ ン、マッピングデータが予め格納されていない余剰領域 である場合には、開発当初のインストラクション、マッ ピングデータがそのまま保存されることになるので、コ ンピュータのために開発されたソフトウェア資産および ハードウェア資産、即ち、基本命令セットにより制御可 能なソフトウェア、周辺機器等を有効利用することがで き、しかも余剰領域に格納された新たなインストラクシ ョン、マッピングデータに基く処理をも遂行することが できる。

ションを取込んでプログラムメモリの余剰領域に格納す るとともに、プログラム格納アドレスに対応するマッピ ングデータをマッピングメモリに格納するロードインス トラクションを有しており、マッピングデータが上記口 ードインストラクションに対応するマッピングデータを 有している場合には、マッピングデータに基いてロード インストラクションを指定し、プログラムメモリから読 出して実行することにより、外部媒体からインストラク ションおよびマッピングデータを取込むことができ、そ の後は、取込まれたインストラクションを指定すること

により所望の処理を遂行させることができる。

さらに、プログラムメモリが初期化時に外部媒体からイ ンストラクションを取込んで格納するものであるととも に、マッピングメモリが各プログラム格納アドレスに対 応するマッピングデータを格納するものである場合に は、初期化時に自動的に外部媒体からインストラクショ ンおよびマッピングデータが取込まれるので、インスト ラクションおよびマッピングデータを取込ませるために 特別の処理を行なう必要がなくなるとともに、外部媒体 を変更するだけで、コンピュータ自体を任意の基本命令 セットを有する状態にすることができる。したがって、 システムに組込まれた周辺機器の種類等に最適な基本命 令セットを有するコンピュータが簡単に得られることに なる。

#### <実施例>

20

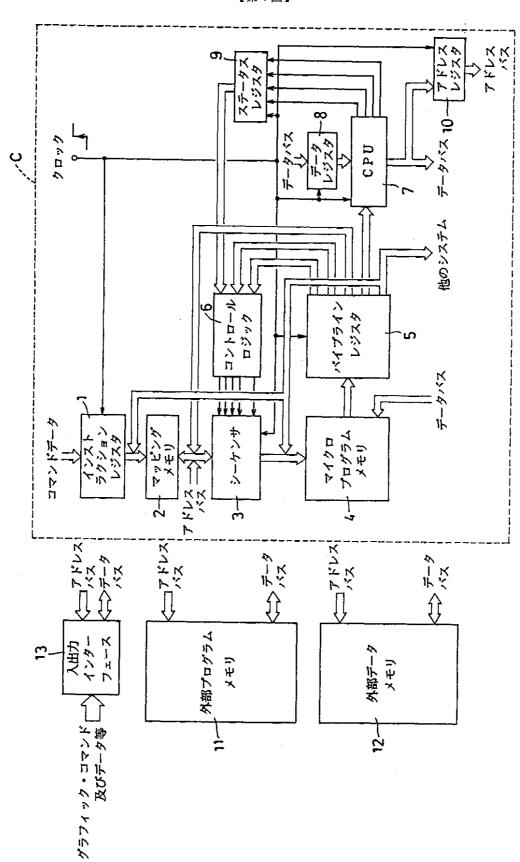

以下、実施例を示す添付図面によって詳細に説明する。 第1図はこの発明のコンピュータの一実施例を示すブロ ック図であり、外部から供給されるコマンドデータを保 持するインストラクションレジスタ(1)と、インスト ラクションレジスタ(1)の内容が読出しアドレスデー タとして供給される、データの書込みが可能なマッピン グメモリ(2)と、マッピングメモリ(2)から出力さ れるアドレスデータ、後述するパイプラインレジスタ (5)から出力されるアドレスデータ、または他の構成 要素から供給されるアドレスデータが供給されるととも に、後述するコントロールロジック(6)から出力され るシーケンサ制御データに基づいて出力データが選択さ れるシーケンサ(3)と、シーケンサ(3)からの出力 データが読出しアドレスとして供給される、データの書 40 込みが可能なマイクロプログラムメモリ(4)と、マイ クロプログラムメモリ(4)から読出されたインストラ クションが供給されるパイプラインレジスタ(5)と、 パイプラインレジスタ(5)からの出力データおよび後 述するステータスレジスタ(9)から出力されるステー タスデータに基づいてシーケンサ制御データを生成する コントロールロジック(6)と、パイプラインレジスタ (5)から出力されるインストラクションおよびデータ レジスタ(8)から出力されるデータに基づいて必要な 処理を行なう中央演算処理装置(以下、CPUと略称す

また、プログラムメモリが、外部媒体からインストラク 50 る)(7)とを有している。そして、上記パイプライン

30

レジスタ(5)からの出力データをマッピングメモリ (2) およびマイクロプログラムメモリ(4) に供給し ているとともに、外部プログラムメモリ(11)、外部デ ータメモリ(12)に格納されているインストラクション をマイクロプログラムメモリ(4)に供給している。ま た、他の構成要素から供給されるアドレスデータはシー ケンサ(3)のみならずマッピングメモリ(2)にも供 給されている。さらに、上記CPU(7)から出力される ステータスデータがステータスレジスタ(9)に供給さ れている。このステータスレジスタ(9)に供給される ステータスデータは、CPU(7)において現在実行して いるマイクロインストラクションに含まれているステー タスビットであり、このステータスビットがステータス レジスタ(9)に一時的に保持され、ステータスレジス タ(9)からは直前に実行されたマイクロインストラク ションに含まれていたステータスビットがステータスデ ータとして出力される。

尚、(10)はCPU(7)からの出力データに基いてアド レスデータを出力するアドレスレジスタであり、(13) は入出力インターフェースであり、上記インストラクシ ョンレジスタ(1)、マッピングメモリ(2)、シーケ ンサ(3)、マイクロプログラムメモリ(4)、パイプ ラインレジスタ(5)、コントロールロジック(6)、 CPU(7)、データレジスタ(8)、ステータスレジス タ(9)およびアドレスレジスタ(10)でコンピュータ (C)が構成されている。そして、上記コンピュータ (C) は少なくとも汎用コンピュータと同一の外部イン ターフェースを有しているとともに、汎用コンピュータ と同一のインストラクションに従って動作するように設 計されている。

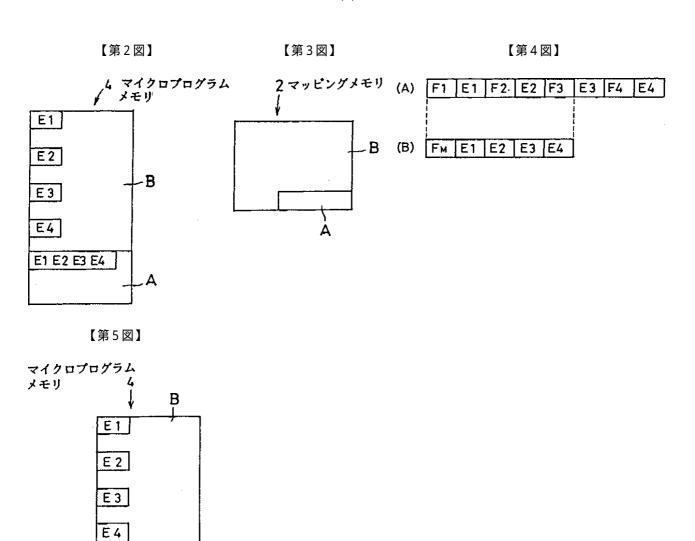

さらに詳細に説明すると、上記マッピングメモリ(2) は、インストラクションレジスタ(1)の内容が読出し アドレスとして供給され、パイプラインレジスタ(5) からの出力データが書込みアドレスとして供給されるも のであり、しかも外部プログラムメモリ(11)または外 部データメモリ(12)から供給されるアドレスデータが アドレス未使用領域(第2図中領域A参照)に格納され るようにしている。上記マイクロプログラムメモリ (4)はシーケンサ(3)からの出力データが読出しア ドレスとして供給され、パイプラインレジスタ(5)か らの出力データが書込みアドレスとして供給されるもの であり、しかも外部プログラムメモリ(11)または外部 データメモリ(12)から供給されるインストラクション がプログラム未使用領域(第3図中領域A参照)に格納 されるようにしている。

尚、上記マイクロプログラムメモリ(4)の残余の領域 Bには予め設定されている基本命令に対応するインスト ラクションが格納されており、上記マッピングメモリ (2)の残余の領域 B には上記各インストラクションの 格納アドレスを示すアドレスデータが格納されている。

上記の構成のコンピュータの動作は次のとおりである。 予め設定されている基本命令に基く処理を行なわせる場 合には、インストラクションレジスタ(1)に保持され ている制御コマンドをマッピングメモリ(2)に供給す ることにより制御コマンドに対応するアドレスデータを 読出し、シーケンサ(3)に供給するので、シーケンサ (3)から出力されるアドレスデータに基づいてマイク ロプログラムメモリ(4)から該当するインストラクシ ョンを読出し、パイプラインレジスタ(5)を通してCP ∪(7)に供給することにより、データレジスタ(8) から出力されるデータに対して所定の処理を施すことが できる。また、基本命令に基づく処理を行なうことがで きるので、基本命令に適用可能な周辺機器はそのまま使 用することができる。

したがって、インストラクションE1,E2,E3,E4に基づく 処理をこの順に実行する場合には、第4図Aに示すよう に、第1回目のインストラクションフェッチF1によりイ ンストラクションE1をフェッチして実行し、第2回目の インストラクションフェッチF2によりインストラクショ ンE2をフェッチして実行し、第3回目のインストラクシ ョンフェッチF3によりインストラクションE3をフェッチ して実行し、第4回目のインストラクションフェッチF4 によりインストラクションE4をフェッチして実行しなけ ればならず、全体としての処理所要時間中に占めるイン ストラクションフェッチ時間の割合いが大きくなるの で、処理能力が低下してしまう。特に上記一連のインス トラクションE1,E2,E3,E4の実行頻度が高い場合には、 処理能力の低下が著しくなってしまう。

しかし、上記の構成のコンピュータ(C)においては、 マイクロプログラムメモリ(4)の領域Aに新たなイン ストラクションを設定することができるのであるから、 予め外部プログラムメモリ(11)または外部データメモ リ(12)に新たな1つのインストラクションE1 E2 E3 E 4を格納しておいて、パイプラインレジスタ(5)から の出力データを書込みアドレスとしてマイクロプログラ ムメモリ(4)に供給することにより上記インストラク ションE1 E2 E3 E4を領域Aに格納することができる。 そして、パイプラインレジスタ(5)からの出力データ を書込みアドレスとしてマッピングメモリ(2)に供給 40 することにより外部プログラムメモリ(11)または外部 データメモリ(12)からアドレスデータを取込んで格納 することができる。

したがって、以上のようにして新たなインストラクショ ンおよびアドレスデータがそれぞれマイクロプログラム メモリ(4)の領域A、マッピングメモリ(2)の領域 Aに格納された後は、インストラクションE1 E2 E3 E4 に対応する制御コマンドをインストラクションレジスタ (1)を通してマッピングメモリ(2)に供給するだけ でよく、第4図Bに示すように、シーケンサ(3)から 出力される読出しアドレスに基づいて1回のインストラ

クションフェッチFMを行なうだけで、第4図Aに示す処 理と同じ処理を行なうことができるインストラクション E1 E2 E3 E4をフェッチすることができる。この結果、 全体としての処理所要時間中に占めるインストラクショ ンフェッチ時間の割合いを著しく小さくすることがで き、処理能力を著しく向上させることができる。特に新 たに格納されたインストラクションの実行頻度が高い場 合には、処理能力を一層向上させることができる。 第5図はマイクロプログラムメモリ(4)の他の構成を 示す概略図であり、上記実施例と異なる点は、領域Aに 10 外部プログラムメモリ(11)または外部データメモリ (12) からマイクロインストラクションを取込んでマイ クロプログラムメモリ(4)に格納するためのマイクロ インストラクションELが予め格納されている点のみであ り、他の部分の構成は同一である。

したがって、この場合には、マッピングメモリ(2)に 格納される、取込みのためのハッシュジャンプアドレス FMO, 取込まれるマイクロインストラクションのためのハ ッシュジャンプアドレスFMnおよびマイクロインストラ としてあらかじめ設定しておくだけでよく、シーケンサ (3)により上記マイクロインストラクションELを指定 して読出し、パイプラインレジスタ(5)を通してCPU (7)に供給して所望のマイクロインストラクションを マイクロプログラムメモリ(4)に格納することができ る。尚、上記ハッシュジャンプアドレスFMnおよびマイ クロインストラクション格納アドレスについては、マイ クロインストラクションが格納される毎に自動的に更新 されるようにしてある。

上記何れの実施例のコンピュータにおいても、ソフトウ 30 ェア開発の機能仕様を実現する場合において汎用コンピ ュータのために予め開発されているソフトウェア資産、 デバッグツール等を利用することができるので、短時間 で目標とする機能仕様を達成することができる。そし て、ハードウェア設計においても、汎用コンピュータの ために開発された周辺機器、例えば、CRTコントロー ラ、ディスクコントローラ、DMA、MMU、PIO等を利用す ることができる。さらに予め設定されている基本命令に より利用可能な開発環境が利用可能であるとともに、追 加または修正されるインストラクションにより複数の汎 40 用コンピュータに対するアプリケーションソフトウェア を実行することも可能である。

尚、この発明は上記の実施例に限定されるものではな く、例えば、マッピングメモリ(2)およびマイクロプ ログラムメモリ(4)が、イニシャル・プログラム・ロ ーディング用マイクロプログラムメモリから初期化時に ロードされるものであってもよく、この場合には、イニ シャル・プログラム・ローディング用マイクロプログラ ムメモリを交換することにより基本命令を変更すること が可能になる。

また、上記コンピュータ(C)の外部機器との接続端子 の配列、規格は汎用コンピュータと同一に設定されてい れば、コンピュータ(C)のみを交換するだけで、著し く処理能率が高いシステムを構築することができる。 さらに、上記コンピュータ(C)としては、ビット・ス

10

ライス・プロセッサであることが最も好ましいが、マイ クロプログラム制御されるコンピュータであれば適用可 能である。但し、固定語長プロセッサの場合には、複数 のインストラクションを 1 インストラクション化するこ とはできないが、予め設定されているインストラクショ ン以外のインストラクションを設定することができる。 <発明の効果>

以上のように第1の発明は、所期の機能仕様を満足させ るコンピュータを短期間で開発することができるととも に、既存のソフトウェア資産、ハードウェア資産、開発 環境の有効活用を達成することができ、しかも汎用性を 損なうことなく、インストラクションフェッチ回数削減 に起因する処理能力を向上させることができるという特 有の効果を奏する。

クション格納アドレスをマイクロインストラクションEL 20 第 2 の発明は、開発当初のインストラクション、マッピ ングデータがそのまま保存されることになるので、コン ピュータのために開発されたソフトウェア資産およびハ ードウェア資産、即ち、基本命令セットにより制御可能 なソフトウェア、周辺機器等を全て有効利用することが でき、しかも余剰領域に格納された新たなインストラク ション、マッピングデータに基く処理をも遂行すること に伴なう処理能力の向上をも達成することができるとい う特有の効果を奏する。

> 第3の発明は、マッピングデータに基づいてロードイン ストラクションを指定するだけで簡単に所期の機能仕様 を達成するコンピュータを得ることができるという特有 の効果を奏する。

第4の発明は、インストラクションおよびマッピングデ ータを取込ませるために特別の処理を行なう必要がなく なるとともに、外部媒体を変更するだけで、コンピュー 夕自体を任意の基本命令セットを有する状態にすること ができるという特有の効果を奏する。

#### 【図面の簡単な説明】

第1図はこの発明のコンピュータの一実施例を示すブロ ック図、

第2図はマイクロプログラムメモリの構成を概略的に示 す図、

第3図はマッピングメモリの構成を概略的に示す図、

第4図はインストラクションフェッチとインストラクシ ョン実行との関係を示す概略図、

第5図はマイクロプログラムメモリの他の構成を示す概

- (2) .....マッピングメモリ、

- (4).....マイクロプログラムメモリ

50

【第1図】

FMO FMn 指納ァドレス

Α

EL-