作成日2008/08/16

AlteraのMaxIIで設計しよう!

時代錯誤の回路図によるCPLD設計

信号出力や制御設定値等を出力するためにD/Aコンバータが必要になるケースがあります。しかし、D/Aコンバータは案外高価な電子部品です。

そこで、CPLDに簡単な外付け回路を使うことで実現するD/Aコンバータを紹介します。

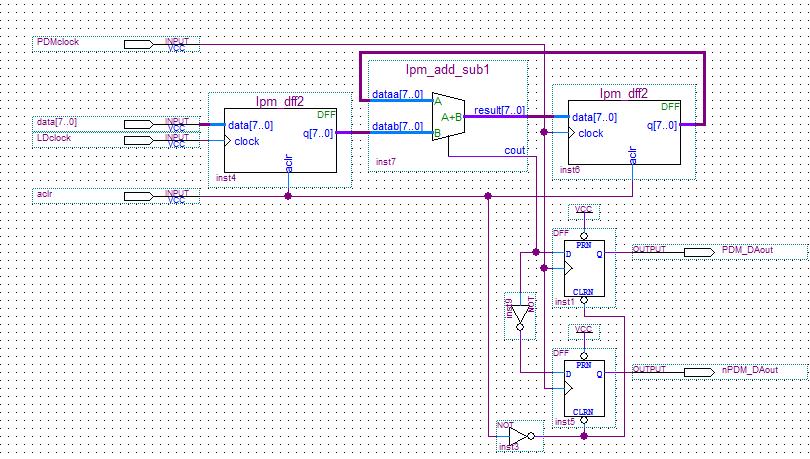

下図の回路はPulse Density Modulation (PDM)と呼ばれるパルス密度でアナログ量を出力するD/Aコンバータ方式です。例では8bit幅のレジスタ2個と加算器1個を用いて8bit精度のD/Aコンバータを実現していますが、ビット幅を変えれば12bit, 16bitのD/Aコンバータも容易に実現することができます。

ノイズ・シェーピング・フィルタと呼ばれるLow Pass Filter(LPF)を用いて高周波成分をカットし、平均値を抽出することにより簡単にアナログ量が得られます。EPM240T100C5で125MHzのクロックを用いた場合、100kHzくらいまで出力することができます。

通常は、PDM_DAoutをLPFに供給するだけでよいのですが、本回路例では、バイポーラ出力を得るために反転出力も用意しています。LPFのカットオフ周波数はビット精度や帯域幅に応じて適宜設計を変更する必要があります。

8bitのD/Aコンバータの場合には総Logic Element数は26です。参考までに12bitのD/Aコンバータの場合には総Logic Element数は38、16bitのD/Aコンバータの場合には総Logic Element数は50です。市販のD/Aコンバータを使う場合と比較すると、1/4以下にコストダウンできる計算になります。

この方式ならオフセット調整のような用途でもディジタル化が容易に行えます。

注意事項: lpm_add_subにはパイプライン化オプションがあり、clockを入れることが可能ですが、これを利用すると

不具合を生じるので必ずlpm_dffをレジスタとして使用してください。

【シミュレーション結果】

【外付けノイズ・シェーピング・フィルタの回路例】

PDM変調に伴う高調波成分を除去するためにLow Pass Filterを用います。このフィルタはノイズ・シェーピング・フィルタとも呼ばれます。カット・オフ周波数は適宜設計変更を行う必要があります。

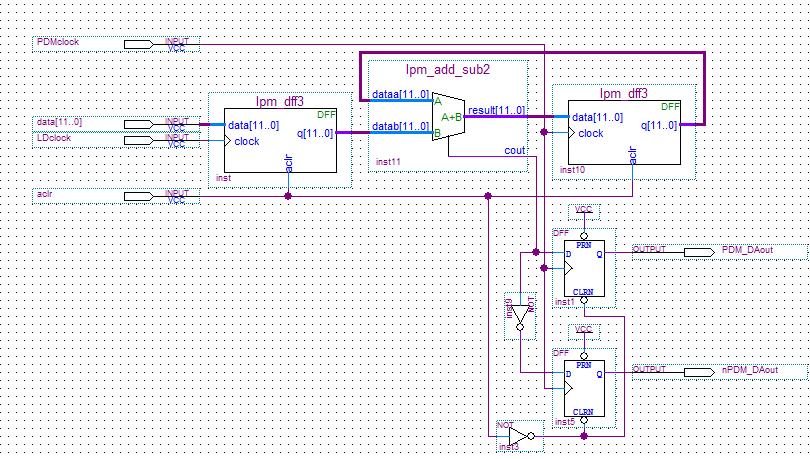

【参考回路図1】

12bitD/Aコンバータの例

ビット幅を12bitに変更しただけです。

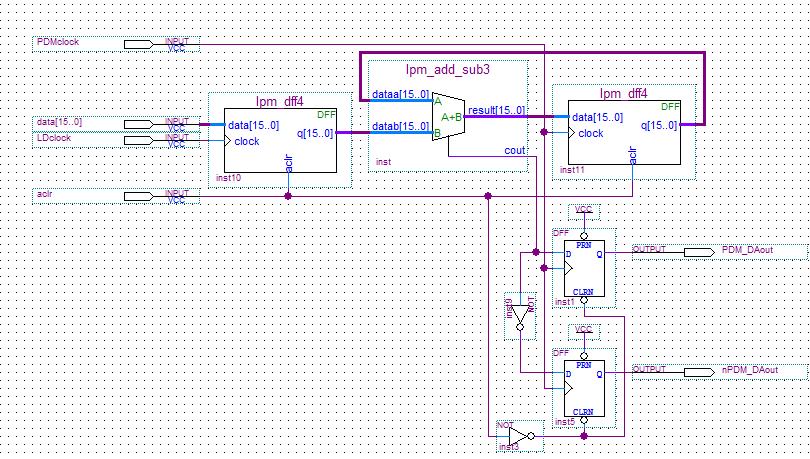

【参考回路図2】

16bitD/Aコンバータの例

ビット幅を16bitに変更しただけです。