作成日2008/08/16

AlteraのMaxIIで設計しよう!

時代錯誤の回路図によるCPLD設計

調歩同期式シリアル通信用レシーバーの回路設計例を示します。

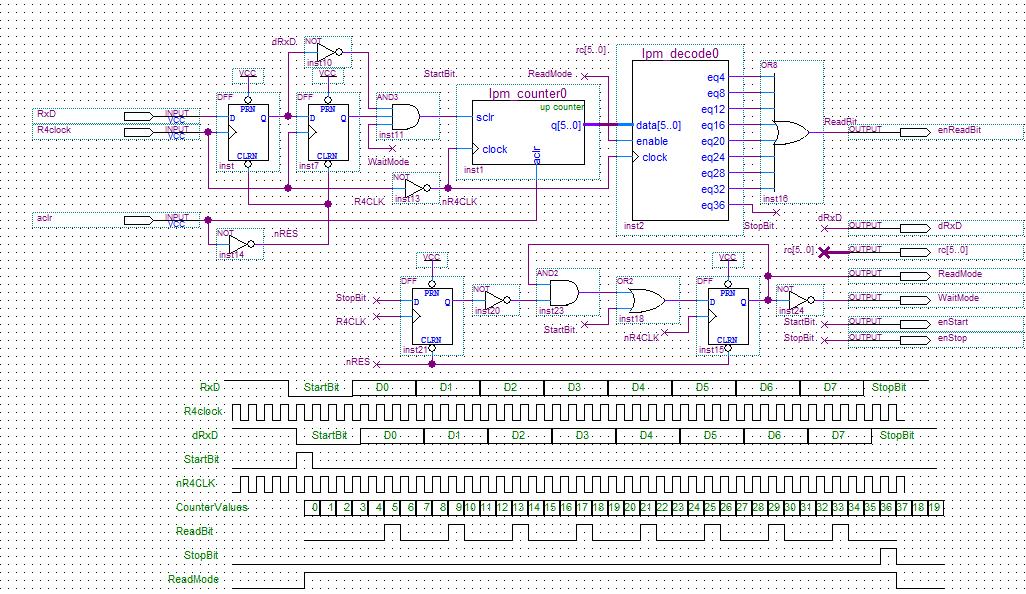

本例では、通信用ボーレート・クロックの4倍のクロックの供給を受けて、スタート・ビットの検出を行い、スタート・ビットの検出に同期させてシリアルに受信データを読み取るためのイネーブルを生成しています。応用例に示すように外部に8bitのシフト・レジスタを接続しておき、ReadBitイネーブルがHighのタイミングで読み込みます。WaitModeに変わる瞬間にシフトレジスタの値を別の8bitのレジスタにコピーします。

シミュレーションは入力設定の関係で1Mbpsで行いましたが問題なく動作しています。

SerialInputモジュールはわずか19logic elementsです。応用例のSerialReceiverモジュールは19200bpsでコンパイルしたところ51logic elementsでした。

【シミュレーション結果】

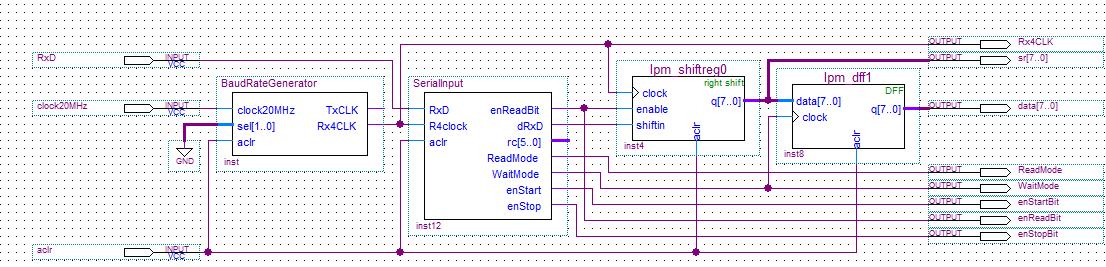

【応用例】